Die theoretischen Designregeln allein garantieren keine EMV-robuste Leiterplatte; die wahre Zuverlässigkeit entsteht erst durch ein fertigungsgerechtes Design, das die physikalischen Realitäten der Produktion von Anfang an berücksichtigt.

- Der Lagenaufbau (Stackup) ist das Fundament der Signalintegrität und hat einen grösseren Einfluss auf die EMV-Performance als das Routing einzelner Leiterbahnen.

- Die Wahl der Oberflächenveredelung (z. B. ENIG vs. HAL) und die unnötige Verschärfung von Toleranzen sind oft übersehene, aber kritische Faktoren, die über Kosten und Ausfallsicherheit in der Serie entscheiden.

Empfehlung: Integrieren Sie die Prinzipien des Design for Manufacturability (DFM) von der ersten Minute an in Ihren Entwicklungsprozess. Analysieren Sie Ihr Design nicht erst am Ende, sondern kontinuierlich aus der Perspektive des Fertigers.

Sie haben Wochen damit verbracht, das perfekte Layout für Ihre neue High-Speed-Baugruppe zu entwickeln. Jede Leiterbahn ist optimiert, die Bauteile sind platziert, die Simulationen sehen vielversprechend aus. Doch der erste Prototyp fällt bei den EMV-Messungen durch. Das Rauschen ist zu hoch, die Signale sind instabil. Eine frustrierende und allzu häufige Erfahrung für viele Hardware-Entwickler und PCB-Designer. Die üblichen Ratschläge sind schnell zur Hand: Leiterbahnen kurz halten, eine durchgehende Massefläche verwenden, analoge und digitale Bereiche trennen. Diese Grundregeln sind wichtig, aber sie kratzen nur an der Oberfläche.

Als CAM-Ingenieur an der Schnittstelle zwischen Design und Fertigung sehe ich täglich die Lücke zwischen der theoretischen Perfektion im CAD-Tool und der physikalischen Realität der Produktion. Viele EMV-Probleme entstehen nicht durch schlechtes Design per se, sondern durch ein Design, das die realen Prozesse und Toleranzen der Leiterplattenherstellung ignoriert. Ein Design, das auf dem Papier funktioniert, kann in der Fertigung zu einer „Kostenfalle“ werden, die teure Redesigns und Verzögerungen im Projektplan nach sich zieht. Der deutsche Leiterplattenmarkt ist ein entscheidender Teil der europäischen Elektronikindustrie, und die Fähigkeit, robuste und fertigbare Designs zu liefern, ist ein entscheidender Wettbewerbsvorteil.

Die wahre Lösung liegt nicht in einer weiteren obskuren Designregel, sondern in einem fundamentalen Perspektivwechsel: Sie müssen beginnen, wie ein Hersteller zu denken. Es geht nicht nur darum, was Ihr CAD-Programm erlaubt, sondern darum, was am Ende stabil und wiederholgenau aus der Ätzanlage, der Presse und der Galvanik kommt. Dieser Artikel führt Sie durch die entscheidenden, aber oft übersehenen Aspekte des Multilayer-Designs aus der Sicht der Fertigung. Wir werden analysieren, wo die wirklichen EMV- und Kostenfallen lauern und wie Sie sie von vornherein vermeiden, um robuste, zuverlässige und kosteneffiziente Leiterplatten zu entwickeln.

Dieser Leitfaden ist strukturiert, um die häufigsten und kostspieligsten Fehler im Designprozess von Multilayer-Leiterplatten zu beleuchten. Jede Sektion adressiert eine spezifische Frage, die an der kritischen Schnittstelle zwischen Design-Intention und Fertigungsrealität entsteht.

Inhaltsverzeichnis: EMV-sicheres PCB-Layout aus der Sicht des Fertigers

- Warum funktionieren Ihre High-Speed-Signale nicht, wenn der Lagenaufbau falsch ist?

- ENIG oder HAL: Welches Finish verhindert Lötfehler bei Fine-Pitch-Bauteilen?

- Platine falten oder Kabel stecken: Was ist bei engen Bauräumen zuverlässiger?

- Der Designfehler, der die Serienfertigung Ihrer Platine 30% teurer macht

- Wann lohnt sich der Eilservice für 48h-Lieferung trotz doppelter Kosten?

- Warum versagt Standard-FR4-Material bei Hochfrequenzanwendungen?

- Fräsen oder 3D-Druck: Welches Verfahren liefert bei Kleinserien die bessere Oberflächengüte?

- Wie halten Sie Fertigungstoleranzen im Mikrometerbereich bei steigendem Kostendruck ein?

Warum funktionieren Ihre High-Speed-Signale nicht, wenn der Lagenaufbau falsch ist?

Viele Designer konzentrieren sich exzessiv auf das Routing einzelner High-Speed-Leiterbahnen, während sie dem Lagenaufbau (Stackup) nur sekundäre Bedeutung beimessen. Das ist ein fundamentaler Fehler. Der Lagenaufbau ist das Fundament Ihrer Signalintegrität. Ein schlecht geplanter Stackup kann selbst das perfekteste Routing zunichtemachen. Der Grund liegt in der Physik der elektromagnetischen Felder: Bei hohen Frequenzen fliesst der Rückstrom nicht den Weg des geringsten Widerstands, sondern den Weg der geringsten Induktivität. Das bedeutet, er will direkt unter der Signalleiterbahn auf der benachbarten Referenzlage (Masse- oder Versorgungslage) fliessen.

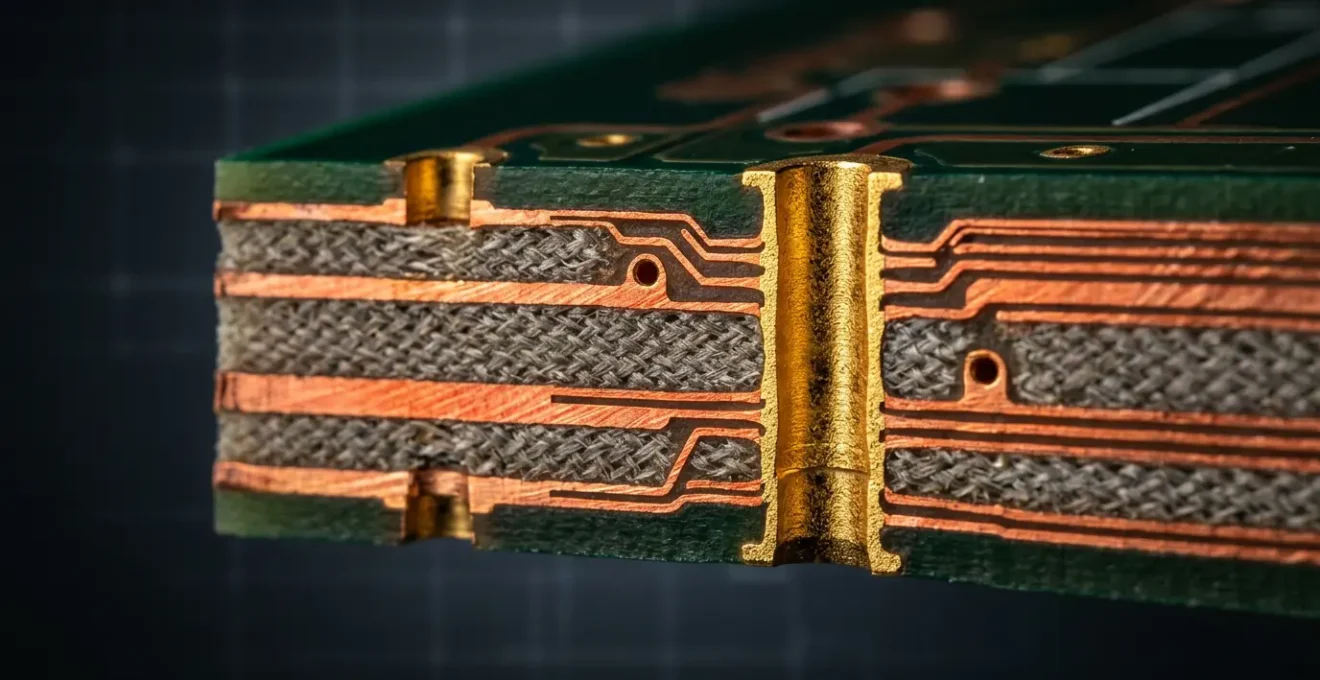

Ein guter Stackup sorgt für eine starke elektromagnetische Kopplung zwischen der Signallage und ihrer Referenzlage. Dies wird durch einen minimalen Abstand (dünnes Prepreg/Core) erreicht. Diese enge Kopplung minimiert die Schleifenfläche, die das Signal und sein Rückstrom bilden. Eine kleine Schleifenfläche bedeutet weniger Induktivität, was zu weniger Rauschen (EMI-Abstrahlung) und einer besseren Signalqualität (weniger Übersprechen) führt. Ein häufiger Fehler ist es, Masse- und Versorgungslagen willkürlich zu platzieren, anstatt sie gezielt als Referenzebenen für kritische Signale zu nutzen. Laut aktuellen Marktstudien hat Deutschland einen Marktanteil von 22% am europäischen Leiterplattenmarkt, was die hohe Dichte an anspruchsvollen High-Speed-Designs unterstreicht.

Die charakteristische Impedanz einer Leiterbahn wird direkt vom Lagenaufbau bestimmt – also von der Leiterbahnbreite, der Dicke und der Dielektrizitätskonstante des Materials sowie dem Abstand zur Referenzebene. Jede Abweichung in der Fertigung von den im Design angenommenen Werten führt zu Impedanzsprüngen, die Signalreflexionen und damit eine Verschlechterung der Signalqualität verursachen. Ein solider, mit dem Hersteller abgestimmter Lagenaufbau ist daher keine Option, sondern eine zwingende Notwendigkeit für jedes erfolgreiche High-Speed-Design.

ENIG oder HAL: Welches Finish verhindert Lötfehler bei Fine-Pitch-Bauteilen?

Die Wahl der Oberflächenveredelung wird oft als letzter, rein kostengetriebener Schritt im Designprozess behandelt. Doch gerade bei modernen Baugruppen mit Fine-Pitch-Bauteilen (geringer Pin-Abstand) und BGAs hat die Oberfläche einen dramatischen Einfluss auf die Lötqualität, Zuverlässigkeit und letztendlich auf die Ausbeute in der Serienfertigung. Die zwei gängigsten Optionen sind HAL (Hot Air Leveling) und ENIG (Electroless Nickel Immersion Gold).

HAL ist kostengünstig, führt aber zu einer naturgemäss unebenen Oberfläche mit variabler Schichtdicke. Für Bauteile mit grossen Pin-Abständen mag das ausreichen, aber bei Fine-Pitch-Komponenten führt diese Unebenheit zu Problemen: unzureichende Benetzung, Lötbrücken oder offene Lötstellen (Head-in-Pillow-Effekt). ENIG erzeugt hingegen eine extrem flache und gleichmässige Oberfläche. Diese Koplanarität ist essenziell, damit die winzigen Lotdepots auf dem Pad und die Lötperlen des BGA-Bauteils im Reflow-Prozess perfekt miteinander verschmelzen können. Die dünne Goldschicht schützt das darunterliegende Nickel vor Oxidation und sorgt für eine exzellente Lötbarkeit und eine lange Lagerfähigkeit von bis zu 12 Monaten.

Die folgende mikroskopische Aufnahme verdeutlicht den Unterschied in der Oberflächentextur zwischen den beiden Verfahren. Während die HAL-Oberfläche eine wellige Struktur aufweist, ist die ENIG-Oberfläche spiegelglatt.

Der höhere Preis von ENIG ist also keine Ausgabe, sondern eine Investition in Prozesssicherheit und Zuverlässigkeit. Bei komplexen Baugruppen mit teuren Komponenten übersteigen die Kosten für Fehlersuche, Reparatur und mögliche Feldausfälle die anfängliche Einsparung durch HAL bei Weitem. Die Entscheidung für die richtige Oberfläche ist ein klassisches Beispiel für fertigungsgerechtes Design.

Die folgende Tabelle fasst die wichtigsten Unterschiede zusammen, die für Ihre Entscheidung relevant sind. Wie der Vergleich für deutsche Industrieanwendungen zeigt, ist die Wahl kontextabhängig.

| Eigenschaft | ENIG | HAL |

|---|---|---|

| Schichtdicke | 4-9µ Nickel, 0.05-0.1µ Gold | Variable Dicke |

| Oberfläche | Sehr flach, ideal für SMD/HDI | Uneben, für radiale Bestückung |

| Lagerzeit | Bis zu 12 Monate | Begrenzte Lagerzeit |

| Mehrfachlötbarkeit | Sehr gut | Eingeschränkt |

| Kosten | Höher | Attraktiv für einfache Anwendungen |

Platine falten oder Kabel stecken: Was ist bei engen Bauräumen zuverlässiger?

In modernen, immer kleiner werdenden Geräten ist der Bauraum extrem begrenzt. Entwickler stehen oft vor der Wahl: Verbinde ich zwei starre Leiterplatten mit einem Flachbandkabel und Steckern oder setze ich auf eine integrierte Starrflex- oder Semiflex-Lösung? Auf den ersten Blick scheint die Kabel-Stecker-Kombination günstiger und flexibler. Aus der Perspektive der Fertigung und der langfristigen Zuverlässigkeit ist dies jedoch oft ein Trugschluss.

Jede Steckverbindung ist eine potenzielle Fehlerquelle. Vibrationen, thermische Zyklen und Feuchtigkeit können zu Kontaktproblemen führen. Die manuelle Montage von Kabeln ist zudem fehleranfällig und erhöht die Montagekosten. Eine Starrflex-Leiterplatte, die starre und flexible Bereiche in einer einzigen, nahtlosen Einheit kombiniert, eliminiert diese Fehlerquellen vollständig. Es gibt keine Stecker, keine Kabel, keine Montageschritte – nur eine einzige, hochintegrierte Komponente. Dies führt zu einer drastisch erhöhten mechanischen Zuverlässigkeit.

Aus EMV-Sicht ist der Vorteil noch gravierender. Bei einer Starrflex-Lösung behalten die Leiterbahnen im flexiblen Teil ihre definierte Impedanz und ihre Referenzierung zu einer benachbarten Massefläche bei. Ein Flachbandkabel hingegen agiert oft als ungewollte Antenne, die Störungen abstrahlt oder empfängt, insbesondere wenn keine adäquate Schirmung vorhanden ist. Die Rückstrompfade sind undefiniert, was bei High-Speed-Signalen zu massiven Problemen mit der Signalintegrität führt. PCB Systems Deutschland betont, dass alle Arten von Leiterplatten, wie Starr, Flex, Starr-Flex, Semi-Flex, heute mit modernsten Technologien gefertigt werden können, was diese Lösungen zugänglicher macht.

Die höheren Initialkosten einer Starrflex-Leiterplatte müssen gegen die Gesamtkosten (Total Cost of Ownership) abgewogen werden. Wenn man die eingesparten Kosten für Stecker, Kabel, Montage und potenzielle Feldausfälle mit einrechnet, ist die integrierte Lösung in anspruchsvollen Anwendungen oft die wirtschaftlichere und technisch überlegene Wahl. Sie ist ein perfektes Beispiel dafür, wie ein Umdenken im Design die Produktqualität fundamental verbessern kann.

Der Designfehler, der die Serienfertigung Ihrer Platine 30% teurer macht

Einer der häufigsten und kostspieligsten Fehler, den wir in der Fertigung sehen, ist nicht offensichtlich im Schaltplan oder Layout zu finden. Es ist die unbedachte oder unnötige Verschärfung von Fertigungstoleranzen. Designer neigen dazu, aus einem falschen Sicherheitsdenken heraus die kleinstmöglichen Leiterbahnbreiten und -abstände, die kleinsten Vias oder extrem enge Ringrest-Vorgaben zu verwenden, die ihr CAD-Tool anbietet. Was im Design wie eine gute Idee für die Miniaturisierung aussieht, ist in der Fertigung eine Kosten- und Ausbeutekatastrophe.

Jeder Leiterplattenhersteller arbeitet innerhalb eines definierten Prozessfensters. Designs, die sich am Rande dieses Fensters bewegen, erfordern einen höheren Prüfaufwand, spezielle Prozesse und führen unweigerlich zu einer geringeren Ausbeute. Jede Platine, die aus der Toleranz fällt, muss verworfen werden. Diese Kosten werden auf den Preis der Gutteile umgelegt. Ein Design, das beispielsweise durchweg die IPC-A-600 Klasse 2 (der Standard für die meisten Industrieprodukte) erfüllt, ist deutlich günstiger zu fertigen als ein Design, das an einigen Stellen ohne Not die Spezifikationen der Klasse 3 (für High-Reliability-Anwendungen wie Luft- und Raumfahrt) fordert. Laut Herstellern wie NextPCB wird die IPC-A-610 Klasse 3 nur auf Anfrage für High-Spec-Anwendungen gefertigt, was den erhöhten Aufwand verdeutlicht.

Fallstudie: DFM-Optimierung in der Praxis

Ein führender deutscher PCB-Hersteller hat eine DFM-Software (Design for Manufacturability) entwickelt, die auf über 15 Jahren Produktionserfahrung basiert. Diese Software analysiert eingehende Kundendesigns automatisch auf potenzielle Fertigungsprobleme. Sie prüft kritische Parameter wie minimale Abstände, Ringreste und die Einhaltung der Designregeln. Stellt sie einen Verstoss fest, der die Ausbeute senken oder das Produkt verteuern würde, generiert sie sofort einen detaillierten Bericht mit Fehlerbeschreibungen und konkreten Lösungsvorschlägen. Dieser proaktive Ansatz verhindert teure Fehler, bevor sie in die Produktion gelangen, und sichert eine reibungslose und kosteneffiziente Fertigung.

Ein weiterer Aspekt ist die Optimierung des Produktionsnutzens. Wenn Ihr Platinenlayout so gestaltet ist, dass es sich schlecht auf einem Standard-Produktionspanel anordnen lässt, entsteht viel ungenutzter Abfall. Eine kleine Anpassung der Platinenabmessungen um wenige Millimeter kann oft den Unterschied ausmachen, ob 10 oder nur 8 Platinen auf einen Nutzen passen – eine direkte Auswirkung auf den Stückpreis von 20%.

Praktische Checkliste: Ihr Design auf Fertigbarkeit prüfen

- Spezifikationen hinterfragen: Benötigen Sie wirklich 0,1 mm Leiterbahnabstand oder reichen auch 0,15 mm? Sprechen Sie mit Ihrem Hersteller über seine Standardprozesse.

- Ringreste maximieren: Verwenden Sie den grösstmöglichen Ringrest, den Ihr Design erlaubt. Dies erhöht die Toleranz gegenüber leichten Verschiebungen beim Bohren.

- Nutzenoptimierung anfragen: Bitten Sie Ihren Hersteller vor der finalen Freigabe um eine Einschätzung zur Nutzenoptimierung. Manchmal kann eine kleine Formänderung grosse Kosten sparen.

- DFM-Regeln anwenden: Nutzen Sie die DFM-Prüffunktionen Ihres CAD-Tools oder die Online-Checker der Hersteller, um Ihr Design proaktiv auf Fertigbarkeit zu analysieren.

- Klassendefinition klären: Definieren Sie klar, welche IPC-Klasse für Ihre Baugruppe erforderlich ist. Fordern Sie Klasse 3 nur, wenn es absolut notwendig ist.

Wann lohnt sich der Eilservice für 48h-Lieferung trotz doppelter Kosten?

Die Frage nach der Lieferzeit ist ein ständiger Balanceakt zwischen Projekt-Deadlines und Budget. Nahezu jeder Hersteller bietet einen Express-Service an, der die Lieferung von Prototypen von den üblichen 5-10 Arbeitstagen auf 24-48 Stunden verkürzt. Dieser Service geht jedoch in der Regel mit einer Verdopplung der Kosten oder mehr einher. Die Entscheidung für oder gegen den Eilservice sollte daher keine reine Bauchentscheidung sein, sondern auf einer kühlen Kosten-Nutzen-Analyse beruhen.

Ein Eilservice lohnt sich in der Regel nur in wenigen, klar definierten Szenarien. Das offensichtlichste ist ein kritischer Time-to-Market. Wenn Sie der Erste auf dem Markt sein müssen oder eine wichtige Messe bevorsteht, bei der ein funktionsfähiger Prototyp präsentiert werden muss, können die Opportunitätskosten einer Verzögerung die Aufschläge für die Expressfertigung bei Weitem übersteigen. Ein weiterer legitimer Grund ist ein Redesign nach einem kritischen Fehler im ersten Prototypenlauf. Hier zählt jeder Tag, um das Projekt wieder auf Kurs zu bringen. Angebote wie die von Aisler, bei denen PCBs in einem Geschäftstag ab $14.05 versprochen werden, zeigen die hohe Wettbewerbsintensität in diesem Segment.

In allen anderen Fällen, insbesondere in frühen Entwicklungsphasen, ist der Standard-Service fast immer die klügere Wahl. Die erzwungene „Wartezeit“ kann produktiv genutzt werden, um das Test-Setup vorzubereiten, die Firmware weiterzuentwickeln oder das nächste Design-Inkrement zu planen. Den Eilservice für den allerersten, oft noch fehlerbehafteten Prototypen zu nutzen, ist meist eine Verschwendung von Budget. Es ist klüger, das Geld in eine zusätzliche Design-Review oder in hochwertigere Bauteile zu investieren.

Die folgende Tabelle stellt die entscheidenden Faktoren gegenüber, um Ihnen eine rationale Entscheidungsgrundlage zu bieten.

| Faktor | Standard (5-7 Tage) | Express (24-48h) |

|---|---|---|

| Lieferzeit | Garantierte Fertigung von Klein- und Musterserien | Express-Service für eilige Projekte |

| Kostenaufschlag | Basispreis | Typisch 100% Aufschlag |

| Anwendungsfall | Normale Entwicklung, frühe Prototypen | Messetermine, Time-to-Market kritisch, Redesign nach Fehler |

Warum versagt Standard-FR4-Material bei Hochfrequenzanwendungen?

FR4 ist das Arbeitspferd unter den Leiterplattenmaterialien: kostengünstig, mechanisch robust und für einen riesigen Bereich von Anwendungen ausreichend. Doch sobald die Signalfrequenzen in den hohen Megahertz- oder sogar Gigahertz-Bereich vordringen, stösst FR4 an seine physikalischen Grenzen. Die Verwendung von Standard-FR4 in HF-Anwendungen ist eine der Hauptursachen für unerklärliche Performance-Probleme.

Das Kernproblem liegt in den dielektrischen Eigenschaften von FR4. Erstens ist die Dielektrizitätskonstante (Dk) von FR4 nicht stabil über die Frequenz. Sie ändert sich mit steigender Frequenz, was die Impedanzkontrolle zu einem Glücksspiel macht. Eine Leiterbahn, die bei 10 MHz eine perfekte 50-Ohm-Impedanz aufweist, kann bei 1 GHz völlig daneben liegen. Zweitens hat FR4 einen relativ hohen Verlustfaktor (tanδ). Dieser Wert beschreibt, wie viel Energie des Signals vom Dielektrikum in Wärme umgewandelt (also absorbiert) wird. Bei hohen Frequenzen führt ein hoher Verlustfaktor zu einer signifikanten Dämpfung des Signals, es verliert an Amplitude und Qualität. Wie technische Analysen zeigen, ist bei Frequenzen über 100 kHz bereits die Induktivität grösser als der Widerstand, was die Materialeigenschaften noch kritischer macht.

Für ernsthafte HF-Anwendungen sind daher spezialisierte Materialien unabdingbar. Diese Materialien, oft von Herstellern wie Rogers, Taconic oder Arlon, zeichnen sich durch folgende Eigenschaften aus:

- Stabile Dielektrizitätskonstante (Dk) über einen breiten Frequenzbereich.

- Niedriger Verlustfaktor (tanδ) für minimale Signaldämpfung.

- Hohe Homogenität in der Materialstruktur, um konsistente Eigenschaften über die gesamte Leiterplatte zu gewährleisten.

Der Einsatz dieser Materialien ist zwar teurer, aber er ist keine Option, sondern eine physikalische Notwendigkeit. Der Versuch, mit Standard-FR4 in einer HF-Anwendung Kosten zu sparen, führt fast immer zu einem nicht funktionierenden Produkt und weitaus höheren Kosten für Fehlersuche und Redesign. Die richtige Materialauswahl ist der erste und wichtigste Schritt für ein erfolgreiches HF-Design.

Fräsen oder 3D-Druck: Welches Verfahren liefert bei Kleinserien die bessere Oberflächengüte?

Die Frage nach der Prototypenfertigung und der Wahl des richtigen Verfahrens für Kleinserien wird oft kontrovers diskutiert. Während der 3D-Druck von Leiterplatten (additives Verfahren) faszinierende Möglichkeiten bietet, bleibt für professionelle Anwendungen, bei denen es auf Präzision und Oberflächengüte ankommt, das Fräsen (subtraktives Verfahren) die überlegene Methode.

Beim 3D-Druck werden leitfähige und isolierende Materialien schichtweise aufgetragen. Dies kann zwar schnell zu einem ersten Funktionsmuster führen, die erreichte Oberflächengüte und Kantenschärfe der Leiterbahnen ist jedoch systembedingt begrenzt. Die Kanten sind oft rau, was bei hohen Frequenzen zu unkontrollierbaren Effekten führen kann (Skin-Effekt). Zudem ist die Auswahl an Materialien und Schichtdicken noch stark eingeschränkt. Für einen schnellen „Proof of Concept“ mag es genügen, für eine verlässliche Kleinserie ist es oft ungeeignet.

Das CNC-Fräsen hingegen startet mit einem vollflächig kupferkaschierten Basismaterial, von dem das unerwünschte Kupfer präzise entfernt wird. Dieses Verfahren ermöglicht extrem glatte Leiterbahnkanten und eine sehr hohe geometrische Genauigkeit. Die Oberflächengüte der Pads ist direkt von der Qualität des Basismaterials abhängig und kann durch nachfolgende Prozesse wie ENIG weiter optimiert werden, um eine perfekte Lötbasis zu schaffen. Deutsche Fertiger wie Alpha-Board organisieren die Leiterplattenfertigung von Prototypen bis zu mittleren Serien mit spezialisierten Partnern, die auf hohe Produktvielfalt und schnelle Liefertermine ausgelegt sind, wobei etablierte subtraktive Verfahren den Standard bilden.

Besonders bei der Frage der Endoberfläche zeigt sich die Überlegenheit traditioneller Verfahren. Die Oberflächengüte ist nicht nur eine Frage der Optik, sondern hat direkte technische Konsequenzen. Beispielsweise ist für Steckkontakte eine harte, abriebfeste Oberfläche nötig. Hier ermöglicht galvanisches Hartgold, Schichtdicken von bis zu 5 µm zu realisieren, was hunderte von Steckzyklen erlaubt. Solche spezifischen und robusten Oberflächen sind mit heutigen additiven Verfahren kaum oder gar nicht in der erforderlichen Qualität darstellbar.

Das Wichtigste in Kürze

- Der Lagenaufbau (Stackup) ist für die EMV-Performance wichtiger als das Routing einzelner Leiterbahnen, da er die kritische Rückstromführung bestimmt.

- Die Wahl der Oberflächenveredelung (z.B. ENIG vs. HAL) ist keine reine Kostenfrage, sondern muss durch die verwendete Bauteiltechnologie (z.B. Fine-Pitch) und die Anforderungen an die Zuverlässigkeit bestimmt werden.

- Design for Manufacturability (DFM) – das Denken in Fertigungsprozessen und -toleranzen von Anfang an – ist die wirksamste Strategie, um Kosten zu senken, die Ausbeute zu erhöhen und die Produktqualität zu sichern.

Wie halten Sie Fertigungstoleranzen im Mikrometerbereich bei steigendem Kostendruck ein?

Der Spagat zwischen steigendem Kostendruck und der Notwendigkeit, immer engere Fertigungstoleranzen im Mikrometerbereich einzuhalten, ist die zentrale Herausforderung in der modernen Leiterplattenfertigung. Die Antwort liegt nicht in einem einzelnen Trick, sondern in einer systematischen Herangehensweise, die auf Standardisierung, Prozesskontrolle und einer klaren Kommunikation zwischen Designer und Hersteller basiert.

Der Grundpfeiler für die Einhaltung von Toleranzen ist die strikte Orientierung an etablierten Industriestandards. Die IPC-Standards (z.B. IPC-6012 für die Qualifikation von Starrleiterplatten oder IPC-A-600 für die Abnahmekriterien) definieren präzise, was unter verschiedenen Klassen (Klasse 1, 2, 3) als „gut“ oder „fehlerhaft“ gilt. Ein professioneller Hersteller richtet seine gesamten Prozesse, von der Materialannahme über die Belichtung und Ätzung bis hin zur Endkontrolle, konsequent an diesen Standards aus. Dies schafft eine gemeinsame Sprache und eine objektive Bemessungsgrundlage. Es stellt sicher, dass sowohl der Designer als auch der Hersteller dasselbe Verständnis von Qualität haben.

Die Einhaltung dieser Standards unter Kostendruck wird durch ein rigoroses statistisches Prozesscontrolling (SPC) und eine kontinuierliche Optimierung der Fertigungsanlagen erreicht. Moderne Anlagen sind mit Sensoren ausgestattet, die Parameter wie die chemische Zusammensetzung der Bäder, Temperaturen oder Belichtungszeiten in Echtzeit überwachen und regeln. Dadurch wird die Prozessvarianz minimiert und sichergestellt, dass das Ergebnis wiederholbar ist. Die Investition in diese Technologie ist hoch, aber sie zahlt sich durch eine höhere Ausbeute und weniger Ausschuss aus, was letztendlich den Kostendruck für den Kunden abfedert.

Wir halten uns streng an wichtige IPC-Standards wie IPC-6012 und J-STD-001. Alle Leiterplatten werden nach IPC-A-600 und IPC-A-610 Klasse 2 gefertigt, Klasse 3 ist auf Anfrage für High-Spec-Anwendungen erhältlich

– NextPCB Germany, Qualitätsstandards deutscher PCB-Fertigung

Letztendlich ist der entscheidende Faktor jedoch die frühzeitige Zusammenarbeit. Anstatt ein Design „über den Zaun zu werfen“ und auf das Beste zu hoffen, sollten Designer die Expertise ihres Herstellers nutzen. Ein kurzer Austausch über kritische Toleranzen oder ein DFM-Check vor der Serienfreigabe kann helfen, kostspielige Anpassungen zu vermeiden und ein Design zu schaffen, das nicht nur auf dem Papier, sondern auch im realen Fertigungsprozess robust und prozesssicher ist.

Häufige Fragen zum Design und zur Fertigung von PCBs als Herzstück der Elektronik

Welche Golddicke für welche Anwendung?

Galvanisches Hartgold ermöglicht 0,8-5µ dicke Schichten. Die Dicke hängt von der Beanspruchung ab. Als Richtwert gilt: 0,4µ Au sind für ca. 20 Steckzyklen ausgelegt, während eine Schicht von 2µ bis zu 500 Steckzyklen standhält.

Wie lange ist die Haltbarkeit verschiedener Oberflächen?

Die Lagerfähigkeit ist ein wichtiger Faktor. Organische Oberflächenschutzmittel (OSP) sind auf etwa 6 Monate begrenzt, da sie mit der Zeit ihre Schutzwirkung verlieren. ENIG (Chemisch Nickel/Gold) hingegen bietet eine exzellente Lagerfähigkeit von bis zu 12 Monaten.

Welche Oberfläche für Mehrfachlötprozesse?

OSP eignet sich nicht für mehrere Lötprozesse. Die organische Schutzschicht zersetzt sich bei Temperaturen über 150°C und bietet daher für den zweiten oder dritten Lötvorgang keinen ausreichenden Schutz mehr vor Oxidation.